Difference between revisions of "FAQ"

(→Does SimWB support 32 and 64 bit MATLAB on Windows and Linux?) |

|||

| Line 9: | Line 9: | ||

===Does SimWB support 32 and 64 bit MATLAB on Windows and Linux?=== | ===Does SimWB support 32 and 64 bit MATLAB on Windows and Linux?=== | ||

| − | Yes, SimWB supports both 32 and 64 bit MATLAB on Windows as well as Linux. SimWB has a small MATLAB/Simulink footprint so SimWB is easily made compatible with the latest version of MATLAB/Simulink offered by the MathWorks.<br style="clear: both" /> | + | Yes, SimWB supports both 32 and 64 bit MATLAB (R2008b and later) on Windows as well as Linux. SimWB has a small MATLAB/Simulink footprint so SimWB is easily made compatible with the latest version of MATLAB/Simulink offered by the MathWorks.<br style="clear: both" /> |

[[File:platform.png]] | [[File:platform.png]] | ||

Revision as of 12:05, 5 December 2011

For questions not answered in this FAQ or if you require additional support using SimWB, please contact us at support@ccur.com.

Contents

General Questions

What are the system requirements for SimWB?

Please see Installation Prerequisites.

Is there a 64 bit version of SimWB?

Yes, there is a 64 bit version of SimWB which can be installed on the 64 bit RedHawk Operating System.

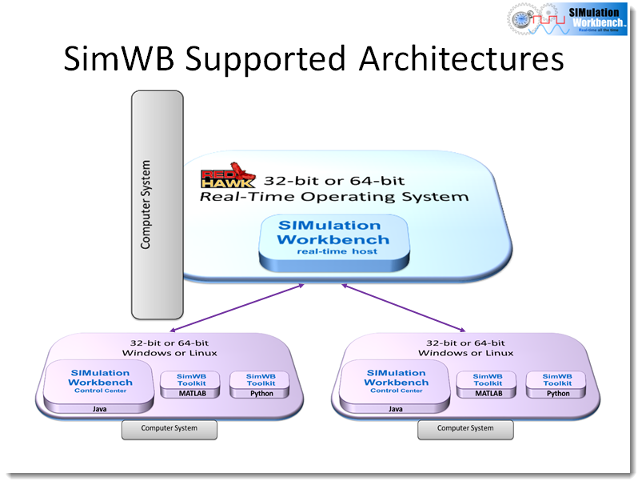

Does SimWB support 32 and 64 bit MATLAB on Windows and Linux?

Yes, SimWB supports both 32 and 64 bit MATLAB (R2008b and later) on Windows as well as Linux. SimWB has a small MATLAB/Simulink footprint so SimWB is easily made compatible with the latest version of MATLAB/Simulink offered by the MathWorks.

Using SimWB

SimWB test and sessions

What is a SimWB test?

A SimWB test is a collection of SimWB resources pulled together to make a runnable configuration.

It is defined with the following resources:

- A RTDB

- The RTDB will define which I/O tasks are run as part of the test run. The set of I/O tasks to run is determined from the RTDB I/O mappings. I.e if a input RTDB item is mapped to a AI64SS channel, an instance of a ai64ss I/O task will be started.

- A test script (optional)

- One or more user or Simulink models (optional)

- A RTDB

What is a SimWB test session?

A test session is a specific runnable instance of a SimWB test. SimWB sessions always belong to a specific test.

A test session can be pre created by the user and then run repeatedly. Run time configuration parameters can be specified independently for each session.

Those parameters are:

- The scheduling method to use to dispatch the simulation loop:

- Default FBS (RCIM) scheduler.

- Software O/S timer.

- Red line scheduler.

- The set of RTDB and Simulink model parameters initial condition.

- The maximum number of overruns to tolerate during the session run.

- The maximum amount of time alloted to process asynchronous RTDB updates from asynchronous I/O tasks.

- Whether the data logger will be run during the session.

- The scheduling method to use to dispatch the simulation loop:

The session will also retain the data logging files corresponding to the RTDB items values that were logged during the run. Be aware that running the session multiple times will overwrite the data that was recorded during a previous run of the session.

A session can also be auto created at startup with default session parameters specified in the GUI interface.

How can I build custom HMI's in SimWB?

How do I create test in SimWB?

You create a test via the SimWB control center. In order to create a test, you just specify the RTDB, the optional test scripts and model(s) that are part of the test.

How do I create a test session in SimWB?

Under the SimWB control Center, select the test for which you want to create a test session. Define all the session specific parameters such as scheduler, initial conditions set, data logging,etc, the session name.

A session can also be automatically be created at test startup by selecting auto-create in the session run/playback tab.

How do I log data during a test/session run?

Simply enable data logging when creating the SimWB test session or when starting the test if you use the session auto create mode.

How do I playback a test in SimWB?

A session that was run with data logging enabled can always be played back.

Select the session you want to playback, select the playback mode and run the session.

SimWB Toolkit for MATLAB

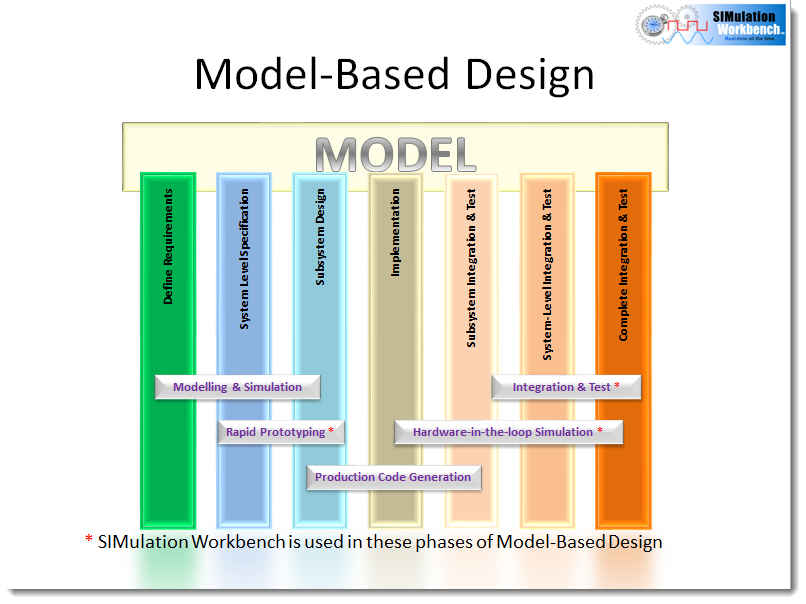

How does SimWB fit into Model Based Design

Model-Based Design is a process that enables faster, more cost-effective development of dynamic systems, including control systems, signal processing, and communications systems. In Model-Based Design, a system model is at the center of the development process, from requirements development, through design, implementation, and testing. The model is an executable specification that is continually refined throughout the development process. After model development, simulation shows whether the model works correctly.

When software and hardware implementation requirements are included, such as fixed-point and timing behavior, you can automatically generate code for embedded deployment and create test benches for system verification, saving time and avoiding the introduction of manually coded errors.

Model-Based Design allows you to improve efficiency by:

- Using a common design environment across project teams

- Linking designs directly to requirements

- Integrating testing with design to continuously identify and correct errors

- Refining algorithms through multidomain simulation

- Automatically generating embedded software code

- Developing and reusing test suites

- Automatically generating documentation

- Reusing designs to deploy systems across multiple processors and hardware targets

The MathWorks is a huge proponent of Model-Based Design and MATLAB and Simulink based tools facilitate in Model-Based Design process. The SIMulation Workbench Toolkit for MATLAB enables Simulink users to generate code from the models and execute and test the model execution in real-time. SIMulation Workbench is typically used in rapid prototyping, hardware-in-loop testing, and integration testing phases of Model-Based Design.

For additional details please see SIMulation Workbench Toolkit.

What is the SimWB Toolkit for MATLAB?

Please see SIMulation Workbench Toolkit.

How do I create an RTDB from a Simulink model?

Please see SIMulation_Workbench_Toolkit#RTDB_Creator_Tab

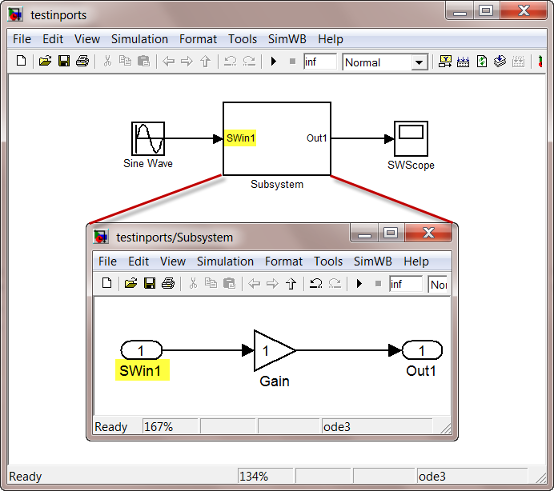

How are subsystem inports and outports handled during SimWB compliant code generation from the SimWB Toolkit?

Inports and Outports are different from other Sources and Sinks in Simulink because they behave differently inside and outside of Simulink subsystems. Subsystem inports and inports have to be connected to other blocks in the subsystem one level higher until we reach the root level (bdroot) of the model. At the root level, inports and outports are indicative of signals external to the Simulink model (i.e they come from the outside world). During SimWB compliant code generation the user can choose the following options:

- Map using block names

- Map "SW" prefixed blocks

If the user chooses the first option i.e. Map using block names, inports and outports are picked up only from the root level(bdroot) to be replaced by RTDB variables in the SimWB compliant generated code. All inports and outports within subsystems are ignored and will not be mapped to RTDB variables. If the user chooses the second option i.e. Map "SW" prefixed blocks, inports and outports with the SW prefix are picked up irrespective of which subsystem they are in within the model. For example, lets consider the model shown here.

The SW prefixed inport "SWin1" is picked and replaced by a RTDB variable during SimWB compliant code generation since we are telling RTW that the "SWin1" port data is essentially going to come from an external source. The RTW engine sees this during code generation and infers that the Sine Wave source block is no longer connected to the "SWin1" port for code generation purposes and so the Sine Wave block is optimized out of the generated code. During code generation, you will see a warning which is expected.

Warning: Unconnected output line found on 'testinports/Sine Wave' (output port: 1)

The following is a snippet of the generated code and we can see that the inport "SWin1" is now mapped to a RTDB variable "in1" which is a part of the the cvtTable structure. There is no mention of the "Sine Wave" block as it has been optimized out during the code generation process.

/* Model output function */

static void testinports_output(int_T tid)

{

/* local block i/o variables */

real_T rtb_SWin1;

/* M-S-Function: '<S1>/SWin1' */

/* M-S-Function Block: <S1>/SWin1 */

rtb_SWin1 = cvtTable.in1 ;

/* Gain: '<S1>/Gain' */

testinports_B.Gain = testinports_P.Gain_Gain * rtb_SWin1;

/* M-S-Function: '<Root>/SWScope' */

/* M-S-Function Block: <Root>/SWScope */

cvtTable.Scope = testinports_B.Gain;

/* tid is required for a uniform function interface.

* Argument tid is not used in the function. */

UNUSED_PARAMETER(tid);

}

SimWB I/O

Is there a list of I/O supported by SimWB?

Please see Wide selection of COTS I/O boards.

Troubleshooting

How do I debug my source code in SimWB using the QT GUI?

![]() Debugging source code under SimWB

Debugging source code under SimWB

SimWB provides the ability to debug models using KDbg. The following steps are needed to start the debugger from SimWB.

- First re-make the code with the –g flag. This is done by modifying the make file in the source code folder on the real-time host. For example:

- Go to "/usr/local/ccursim/projects/RTW.Sources/modelname_ccurt" folder where "modelname" is the name of the model.

- Edit the "modelname.mk" file

- In the General User Options add the –g flag. Approximately line 153 in the MAKE file should now read OPTS = -g

- Use the commands "make –f modelname.mk clean" and "make –f modelname.mk" to remake the model.

- In the SimWB Control Panel start the Run/Playback test GUI

- In the Test Control GUI select the test with the model that was compiled with the –g flag.

- Press the CTRL key on the keyboard and left click the mouse on the Start button. This will open a menu with the NightTrace and the Debug option

- Hover the mouse over the Debug option and this will display a list of User Tasks and System Tasks which one can debug.

- Select the model that you want to debug from the User Tasks list. Upon selection of the model the KDbg GUI will open and stop in the ccurrt_mainC.c file for this model. If the debugger stops in the schedutils.c task it is an indicator that you need to remake the source with the –g file.

- Now you can place debug points in the source code to debug the model. The model is called by the rt_OneStep() function.